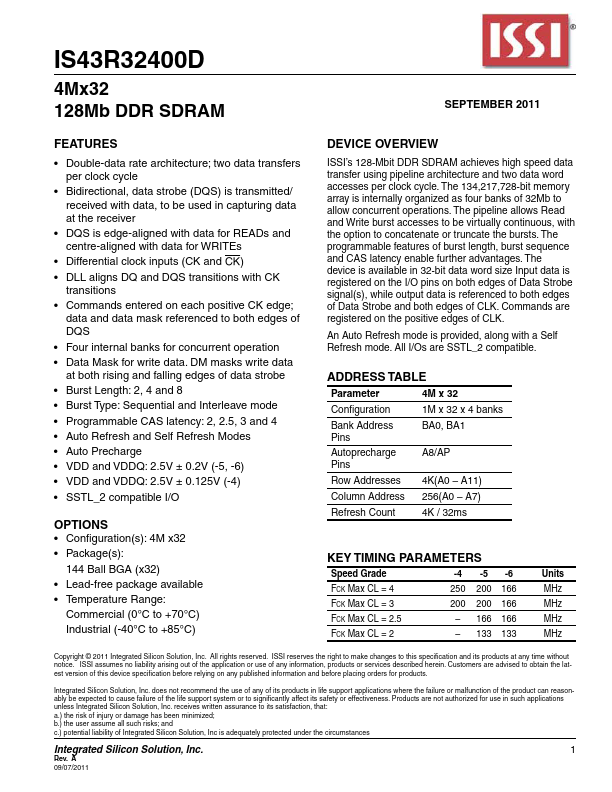

IS43R32400D Overview

Key Specifications

Package: LFBGA

Mount Type: Surface Mount

Pins: 144

Operating Voltage: 2.5 V

Key Features

- Double-data rate architecture; two data transfers per clock cycle

- Bidirectional, data strobe (DQS) is transmitted/ received with data, to be used in capturing data at the receiver

- DQS is edge-aligned with data for READs and centre-aligned with data for WRITEs

- Differential clock inputs (CK and CK)

- DLL aligns DQ and DQS transitions with CK transitions